# Digital Electronics<sup>TM</sup> Final Examination

**More Practice Questions**

| Student Name: _ |              |     |   |

|-----------------|--------------|-----|---|

| Date            | ):           |     | _ |

| Cla             | ss Period: _ |     | _ |

| Tot             | tal Points:  | /50 |   |

| Conv            | erted Score: | /4( | 0 |

Directions: This is a CLOSED BOOK/CLOSED NOTES exam. Select the letter of the response which best completes the item or answers the question. Then record your answer on the answer sheet provided for Part A. After reading a digital meter, a technician obtained a reading of 0.0073 volts. Which of the following numbers is the proper engineering notation for that number? 7.3 m Volts 0.0073 μ Volts 7.3 μ Volts 7.3 K Volts What is the value of the resistor shown below? 3. Silver Brown Blue Orange 160 K Ω ±10 % 360 Ω ±10 % 360 Ω ±5 % 36 K Ω ±5 % In a series circuit, you measure 9 volts across a 300  $\Omega$  resistor. How much current is flowing through the resistor?

300 m Amps

3 m Amps

30 m Amps

33.33 Amps

| 7. | What is the binary equivalent to the d | ecimal number 13 <sub>10</sub> ?   |

|----|----------------------------------------|------------------------------------|

|    | <b>A.</b> (1101 <sub>2</sub> )         | <b>C.</b> 1011 <sub>2</sub>        |

|    | <b>B.</b> (0111 <sub>2</sub> )         | <b>D.</b> 1001 <sub>2</sub>        |

|    |                                        |                                    |

| 9. | What is the binary equivalent to the h | exadecimal number C <sub>H</sub> ? |

|    | <b>A.</b> (1000 <sub>2</sub> )         | <b>C.</b> 1001 <sub>2</sub>        |

|    | <b>B.</b> 0110 <sub>2</sub>            | <b>D.</b> 1100 <sub>2</sub>        |

|    |                                        |                                    |

10. The truth-table shown below represents which of the following gates?

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

**A.** X - Z

**C.** X- O-Z

**B.** X Y Z - Z

**D.** X O-Z

12. The truth-table shown below represents which of the following gates?

**A.** X Y - Z

C.

**B.** X Y - Z

**D.** X

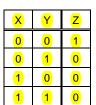

## 13. The gate shown to the right is represented by which of the following truth-tables?

A.

|   | X | Y | Z |

|---|---|---|---|

|   | 0 | 0 | 0 |

|   | 0 | 1 | 0 |

|   | 1 | 0 | 0 |

| Γ | 1 | 1 | 1 |

C.

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

B.

| X | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

D.

| X | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

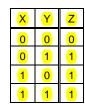

## 14. The gate shown to the right is represented by which of the following truth-tables?

A.

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

C.

B.

| X | Y | Z |  |

|---|---|---|--|

| 0 | 0 | 1 |  |

| 0 | 1 | 1 |  |

| 1 | 0 | 1 |  |

| 1 | 1 | 0 |  |

D.

#### 15. Which of the following is a rule of Boolean algebra?

A.

$$X \bullet \overline{X} = \overline{X}$$

$$\mathbf{B.} \quad \mathbf{X} \bullet \mathbf{X} = \mathbf{X}$$

**D.**

$$X + X = 1$$

### 16. Which of the following is a rule of Boolean algebra?

**A.**

$$A + 1 = A$$

c.

$$A + 1 = 1$$

**B.**

$$A + 0 = 1$$

$$A + \overline{A} = 0$$

17. Which of the following is the simplified equivalent for the Boolean equation shown?

$$F = \overline{Y} + X \overline{Y}$$

F = X Y

F = X

18. Which of the following equations is the un-simplified Sum-Of-Products equation for the truth table shown?

| X | Y | Z | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

- A.  $F = \overline{X} \overline{Y} Z + \overline{X} Y \overline{Z} + X Y \overline{Z}$  C.  $F = \overline{X} \overline{Y} Z + \overline{X} \overline{Y} Z + X Y \overline{Z}$

- $F = \overline{X} \overline{Y} Z + \overline{X} Y \overline{Z} + X \overline{Y} Z \qquad \textbf{D.} \qquad F = X \overline{Y} \overline{Z} + \overline{X} Y \overline{Z} + X Y \overline{Z}$

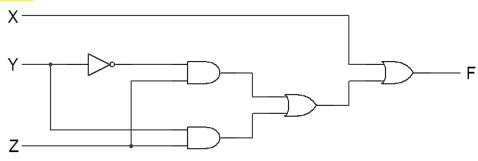

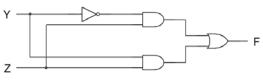

19. Which of the following un-simplified Boolean expressions represent the logic circuit shown below?

- $A. \quad F = X + \overline{Y}Z + \overline{Y}\overline{Z}$

- $\mathbf{C.} \quad \mathbf{F} = \mathbf{X} + \mathbf{Y} \, \overline{\mathbf{Z}} + \mathbf{Y} \, \mathbf{Z}$

- $P = \overline{X} + \overline{Y}Z + YZ$

21. Which of the following is the simplified equivalent for the Boolean equation shown?

$$F = \overline{X + \overline{Y}}$$

$$A. \quad F = \overline{X} Y$$

$$C. \quad F = X \overline{Y}$$

$$B. \quad F = X + \overline{Y}$$

$$F = \overline{X} \overline{Y}$$

22. Which of the following K-Maps has the 1's & 0's properly placed for the function F<sub>20</sub>?

| W | X | Y | Z | F |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

$\overline{W}\overline{X}$   $\overline{W}X$  WX  $W\overline{X}$  $\overline{Y}Z$ A. ΥZ ΥZ

|    |                | $\overline{W}\overline{X}$ | $\overline{W}X$ | WX | $W\overline{X}$ |

|----|----------------|----------------------------|-----------------|----|-----------------|

|    | YZ             | 0                          | 0               | 1  | 0               |

| C. | <del>Y</del> Z | 0                          | 1               | 1  | 0               |

|    | ΥZ             | 1                          | 0               | 0  | 1               |

|    | Y 7            | 1                          | 1               | 0  | 0               |

WX  $\overline{\mathsf{W}}\,\mathsf{X}$ WX WX YZ  $\overline{Y}Z$ B. YZ ΥZ

|    |                            | W X | W X | W X | WX |

|----|----------------------------|-----|-----|-----|----|

|    | $\overline{Y}\overline{Z}$ | 0   | 0   | 0   | 1  |

| D. | <del>Y</del> Z             | 0   | 1   | 0   | 1  |

|    | YZ                         | 1   | 0   | 1   | 0  |

|    | YZ                         | 1   | 1   | 0   | 0  |

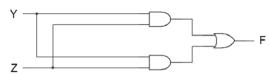

23. Which of the following logic circuits correctly implements the Boolean equation?

$$F = \overline{Y}Z + Y\overline{Z}$$

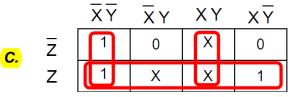

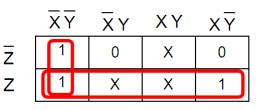

24. Which of the following K-maps is grouped properly and will result in the simplest solution?

D.

A.

$$\overline{Z}$$

$\overline{X}$

$\overline{Y}$

$\overline{X}$

$\overline{Y}$

$\overline{X}$

$\overline{Y}$

$\overline{X}$

$\overline{Y}$

$\overline{X}$

$\overline{Y}$

$\overline{X}$

$\overline{Y}$

$\overline{Y}$

25. Which Boolean equation is in Product-Of-Sums form?

$$A. \quad \mathbf{F} = \mathbf{X} \mathbf{Y} \mathbf{Z} + \mathbf{X} \mathbf{Y} + \mathbf{X} \mathbf{Y} \mathbf{Z}$$

$$F = X Y \overline{Z} + X \overline{Y} + X Y Z$$

**c.**  $F = (X + Y)(X + Z)(\overline{Y} + Z)$

$$B. \quad \mathbf{F} = \mathbf{X} \, \overline{\mathbf{Y}} \, \overline{\mathbf{Z}} + \mathbf{Z} \, (\mathbf{X} + \mathbf{Y})$$

$$F = X Z (Y + Z)(\overline{Y} + Z)$$

26. Which of the following Boolean equation is in Sum-Of-Products form?

$$A. \quad F = A \overline{B} C + \overline{A} B \overline{C} + A \overline{C}$$

$$F = (\overline{A} + B + \overline{C})(\overline{A} + C)(A + \overline{B} + C)$$

$$\mathbf{B.} \quad \mathbf{F} = \overline{\mathbf{A}} \, \mathbf{B} \, \mathbf{C} + \mathbf{A} \, (\overline{\mathbf{B}} + \mathbf{C})$$

$$\overline{\mathbf{P}} = \overline{\mathbf{A}} (\mathbf{B} + \mathbf{C}) + \mathbf{A} (\overline{\mathbf{B}} + \mathbf{C})$$

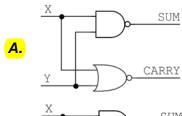

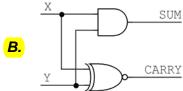

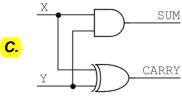

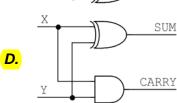

#### 29. Which of the following circuits is a half-adder?

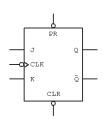

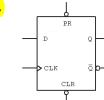

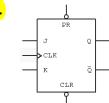

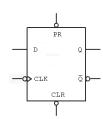

30. Which of the devices shown below is a Negative Edge Triggered D flip-flop?

A.

C.

B.

D.

31. How are the Q and  $\overline{Q}$  outputs of a flip flop affected by setting the active high asynchronous PRESET input to a logic one?

A. No change.

C. Q = 0 and  $\overline{Q} = 1$

**B.** Q = 1 and  $\overline{Q} = 0$

Q = 1 and  $\overline{Q} = 1$

32. How are the Q and  $\overline{Q}$  outputs of a flip flop affected by setting the active low asynchronous CLEAR input to a logic zero?

A. No change.

C. Q = 0 and  $\overline{Q} = 1$

**B.** Q = 1 and  $\overline{Q} = 0$

Q = 1 and  $\overline{Q} = 1$

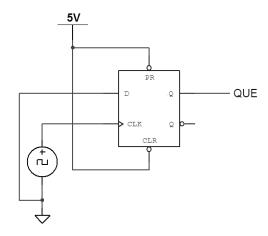

Regardless of its current value, what will happen to the output **QUE** on the next clock pulse?

A. QUE will be low.

- **C.** QUE will toggle.

- **B.** QUE will be high.

- **D.** QUE will not change.

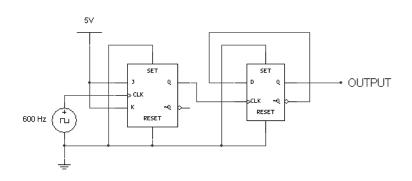

35. Determine the output frequency for the circuit shown to the right.

**A.** 150 Hz.

**C.** 300 Hz.

**B.** 600 Hz.

**D.** 450 Hz.

| 36. |             | at is the minimum numbe<br>nter?        | of flip-flops r | needed to build a Mod-10 Asynchronous                 |

|-----|-------------|-----------------------------------------|-----------------|-------------------------------------------------------|

|     | A.          | 3                                       | C.              | 4                                                     |

|     | B.          | 5                                       | D.              | 10                                                    |

|     |             |                                         |                 |                                                       |

|     |             |                                         |                 |                                                       |

|     |             |                                         |                 |                                                       |

|     |             |                                         |                 |                                                       |

|     |             |                                         |                 |                                                       |

|     |             |                                         |                 |                                                       |

|     |             |                                         |                 |                                                       |

|     |             |                                         |                 |                                                       |

|     |             |                                         |                 |                                                       |

|     |             |                                         |                 |                                                       |

|     |             |                                         |                 |                                                       |

|     |             |                                         |                 |                                                       |

|     |             |                                         |                 |                                                       |

|     |             |                                         |                 |                                                       |

|     |             |                                         |                 |                                                       |

| 39. | Who<br>true |                                         | ates to CMOS    | S gates, which of the following statements is         |

|     | <b>A.</b>   | CMOS gates use more                     | power C.        | CMOS gates are more sensitive to static               |

|     |             | than TTL gates.                         |                 | electricity than TTL gates.                           |

|     | B.          | CMOS gates are <u>faster</u> TTL gates. | than D.         | CMOS gates have a <u>lower margin than TTL</u> gates. |

|     |             |                                         |                 |                                                       |

#### 40. Propagation delay is \_\_

- A. a measure of the ability of a logic gate to drive further logic gates.

- the difference in chip temperature from when the power is off to when the power is on.

- c. the difference between what a logic gate outputs as a valid logic voltage and what the input of the next gates expects to see as a valid logic voltage.

- **D.** the time required for a signal to travel from the input of a logic gate to the output.